# Effect of an Image Plane on Printed Circuit Board Radiation

Robert F. German IBM Corporation Boulder, CO 80301

Henry W. Ott Henry Ott Consultants Livingston, NJ 07039

Clayton R. Paul University of Kentucky Lexington, KY 40506

Abstract- The effect of placing a conducting plane beneath a printed circuit board (PCB) is analyzed. Experimental results illustrate that when the plane was close to the PCB, the ground-noise voltage and radiated emissions were significantly reduced. This conducting plane is called an *image plane* because its equivalent image currents produce these desirable effects. The radiated emissions of attached cables are also shown to be dramatically reduced if the cable wires are correctly attached to the image plane.

# INTRODUCTION

The subject of this paper is the reduction of printed circuit board (PCB) ground-noise and radiation. It has been previously shown that there is a qualitative correlation between ground-noise voltage and radiated emissions [1]. It has also been shown that common-mode currents are the predominant source of radiated emissions from a PCB [2] and that these currents flow on external or peripheral PCB cables [3]. We will discuss three mechanisms that result in PCB radiation: differential-mode loop antenna, common-mode dipole antenna driven by the ground-noise voltage, and common-mode asymmetrical dipole antenna driven by the signal voltage.

This paper presents a very effective method of reducing the ground-noise voltage and radiated emissions from a PCB with or without attached cables. The method consists of placing a conducting plane beneath and close to the PCB. The equivalent image currents of this conducting plane produce radiated fields that tend to cancel the fields from the differential-mode or common-mode currents flowing through the PCB traces. If cables are attached to the traces, the common-mode currents on the cables (and the resulting radiated emissions) can be significantly reduced if the cable wires are correctly attached to the conducting plane.

In addition, the concept of partial inductance is used to derive simple equations that are useful for calculating the inductance of PCB traces.

# THE PROBLEM

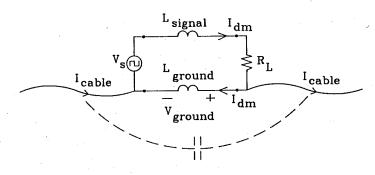

To illustrate the basic problem, consider the PCB traces in Figure 1, which are driven by a source voltage  $V_S$  and terminated with a load resistance  $R_L$ . Wires that simulate cables attached to the PCB are also shown connected to the ends of the ground-return trace. The usual functional current is referred to as differential-mode current  $I_{dm}$  and is equal in magnitude and is oppositely directed in the signal and

ground-return traces. Although this is the intended signal current, it forms a differential-mode loop antenna as it flows through the traces. This loop antenna is one source of radiation from a PCB.

Signal and ground-return traces are usually placed close together to minimize the loop inductance. However, the inductance of each trace is nonzero. If the traces are shorter than a wavelength, this distributed inductance can be replaced with an equivalent lumped inductance for each trace as shown in Figure 1. When the source voltage changes, the resulting change in current causes a voltage to be developed across the inductance of the ground-return trace  $V_{ground} = L di/dt$ . This voltage can drive the cables as a dipole antenna producing a common-mode current  $I_{cable}$ . Note that the capacitance (shown dotted in Figure 1) represents a distributed parasitic capacitance between the two cables that provides a return path for the common-mode current. This is the second source of radiated emissions from a PCB. However, it is not the only mechanism that can produce common-mode current.

To compare the relative magnitude of these two radiation mechanisms, assume that the signal and ground-return traces in Figure 1 are each 7.6 cm (3 inches) long and are spaced 1.3 cm (1/2 inch) apart. These traces each have an inductance of 72 nH and form a loop antenna with an area of  $10 \text{ cm}^2$ . Also assume that the wires connected to the ends of the ground-return trace are each 1.0 m long. Now if the Fourier series of the differential-mode signal current has a 50 MHz component that is 1 mA, a voltage drop of 22.6 mV will be developed across the 72 nH ground-return inductance. Because the 1.0 m cables (20 AWG) have a  $22 - j472 \Omega$  dipole driving-point impedance [4], the 22.6 mV of ground noise will produce  $48 \mu A$  of common-mode current on the cables.

Figure 1. Typical PCB with Attached Cables

The electric field caused by the differential-mode radiation from the PCB loop, calculated using Equation 11-2 on page 301 in [5], is  $22 \mu V/m$  at  $50 \, MHz$  and at a distance of  $3.0 \, m$  from the PCB. The electric field caused by the common-mode radiation from the cable, calculated using Equation 11-7 on page 313 in [5], is  $1,005 \, \mu V/m$ , also at  $50 \, MHz$  and at a distance of  $3.0 \, m$  from the PCB. Hence, the common-mode emission is more than  $33 \, dB$  greater than the differential-mode emission, even though they are produced by the same source: the current flowing around the  $10 \, cm^2$  loop on the PCB.

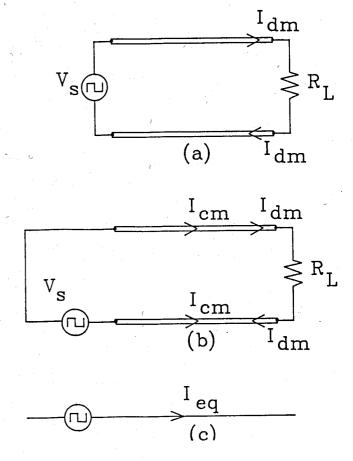

A third source of emissions from a PCB is a common-mode asymmetrical dipole antenna. Consider the PCB circuit in Figure 2a. If the trace separation is much smaller than the length of the traces, the differential-mode current produces relatively little radiation because the fields from these equal and opposite currents tend to cancel. Moreover, if the traces are identical in cross section and the source is centered at one end, the circuit is symmetrical and only the differential-mode currents will flow through the traces. In practice, however, asymmetries usually occur on a two-sided PCB [2].

Consider a source that is connected with unequal-length wires to the signal and ground-return traces in Figure 2b. This is one example of an asymmetrical circuit. The radiation from the differential-mode current tends to cancel as it did for the symmetrical circuit. However, if the trace separation is much smaller than the length of the traces, there will also be common-mode currents that flow in the same direction along each trace [6]. The emissions from these common-mode currents are much greater than the emissions from the differential-mode currents, because the common-mode radiation is additive. These common-mode emissions are also equivalent to the emissions from the asymmetrical dipole in Figure 2c, which is driven by a source that is proportional to the signal voltage [2].

Because common-mode radiation usually is predominant, the first step in reducing PCB emissions is to lower the ground-noise voltage, which is one driving function of the common-mode emissions. This noise voltage can be reduced by lowering the current, increasing the current rise-time, or lowering the ground-return inductance [7]. Once the minimum current and maximum rise-time have been employed, the inductance of the ground-return trace becomes the only remaining parameter to reduce the ground-noise voltage. To understand how to lower the ground-return inductance, one can use the concept of partial inductance [8],[9].

# PARTIAL INDUCTANCE

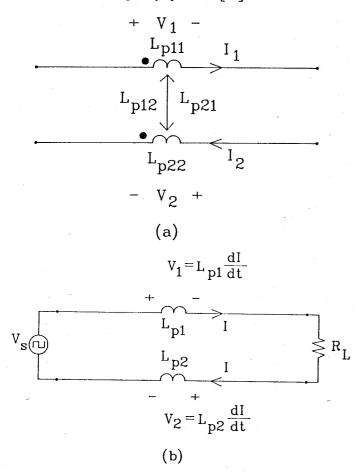

Consider the pair of identical parallel conductors in Figure 3a. This circuit can be represented with partial self-inductances  $L_{p11} = L_{p22}$ , and partial mutual-inductances  $L_{p12} = L_{p21}$  [8], [9]. These inductances are called partial inductances because they are only part of the circuit's total self and mutual inductances. Now the voltage developed across each conductor [8] is

Figure 2. Differential-mode Currents and Common-mode Currents on a PCB

$$V_1 = L_{p11} \frac{dI_1}{dt} - L_{p12} \frac{dI_2}{dt}$$

(1a)

$$V_2 = L_{p22} \frac{dl_2}{dt} - L_{p21} \frac{dl_1}{dt} \,. \tag{1b}$$

Equation (1) reveals that these voltages are a function of the current in the conductor itself and the current in the other conductor. In general, the voltage developed across any conductor is a function of the current in the conductor itself and the current in all proximal conductors [8].

If the conductors in Figure 3a are a signal conductor and the associated ground-return conductor, then  $I_1 = I_2 \equiv I$ , and we may define the *net partial inductance of each conductor* as

$$L_{p1} = L_{p11} - L_{p12} (2a)$$

$$L_{p2} = L_{p22} - L_{p21} (2b)$$

where  $L_{p1} = L_{p2}$ . Once the net partial inductances are determined for a given conductor separation and cross-sectional dimensions, the equivalent circuit in Figure 3b can be constructed and the voltage developed across each conductor calculated using ordinary circuit-analysis techniques. Standard

computer-aided, lumped circuit-analysis programs such as SPICE or ASTAP can be used to solve for the time-domain voltages and their frequency spectrum [10].

Figure 3. Parallel Conductors in Free Space

The net partial inductances in (2) are important quantities because the ground-noise voltage developed across each conductor is simply the net partial inductance multiplied by the change in the current. Because the partial mutual-inductance between the two conductors increases as the distance between the conductors is reduced, whereas the partial self-inductances are unchanged [8],[9], the net partial inductance decreases as the conductors are brought closer together. Hence, the voltage developed across each conductor decreases as the conductors are brought closer together.

For round wires with length l and radius  $\rho$ , such that  $l \gg \rho$ , the low-frequency partial self-inductance is given by Grover [11] as

$$L_{p11} = L_{p22} = \frac{\mu_0 l}{8\pi} + \frac{\mu_0 l}{2\pi} \left[ \ln \frac{2l}{\rho} - 1 \right]$$

(3)

where the first term is the *internal* partial self-inductance, making the last term the *external* partial self-inductance [12]. At high frequencies, the current flows on the surface of the conductor, and the internal inductance becomes negligible. Hence the high-frequency partial self-inductance of a round wire is obtained by eliminating the internal inductance in (3), which leaves

$$L_{p11} = L_{p22} = \frac{\mu_0 l}{2\pi} \left[ \ln \frac{2l}{\rho} - 1 \right]. \tag{4}$$

For conductors of rectangular cross-section with length l, width w, and thickness t, such that  $l \ge w \ge t$ , the low-frequency partial self-inductance given by Grover [11] is

$$L_{p11} = L_{p22} = \frac{\mu_0 l}{2\pi} \left[ \ln \frac{8l}{w + t} - \frac{1}{2} \right]. \tag{5}$$

Because the internal inductance is not isolated in (5), its high-frequency behavior is not obvious. However, the high-frequency partial self-inductance for infinitely thin conductors is given by Kalantarov and Tseitlin [13]:

$$L_{p11} = L_{p22} = \frac{\mu_0 l}{2\pi} \left[ \ln \frac{8l}{w} - 1 \right]. \tag{6}$$

Note that an approximation of the internal partial self-inductance of thin conductors can be obtained by subtracting (6) from (5).

If the conductors in Figure 3b each have a length l and are separated by a distance d, such that  $d \le l$  and d is much larger than the cross-sectional dimensions of the conductors, the mutual inductance between round conductors or PCB traces can both be approximated by the mutual inductance between two filaments [11], which is

$$L_{p12} = L_{p21} = \frac{\mu_0 l}{2\pi} \left[ \ln \frac{2l}{d} - 1 + \frac{d}{l} \right]. \tag{7}$$

The net partial inductance of a thin PCB trace at high frequencies can now be determined by substituting (6) and (7) into (2), which yields

$$L_{p1} = L_{p2} = \frac{\mu_0 l}{2\pi} \left[ \ln \frac{4d}{w} - \frac{d}{l} \right]$$

(8a)

$$L_{p1} = L_{p2} \simeq \frac{\mu_0 l}{2\pi} \left[ \ln \frac{4d}{w} \right] \qquad if \quad d \leqslant l$$

(8b)

with the corresponding round-wire formula being easily obtained by using (4) in place of (6).

The above equations can only be compared to the usual per-unit-length inductance of transmission-line theory if  $d \le l$  because these equations were derived for finite-length conductors, whereas per-unit-length parameters are derived for infinite-length conductors [8].

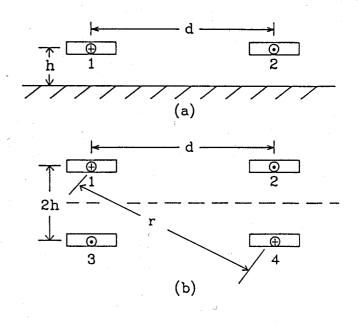

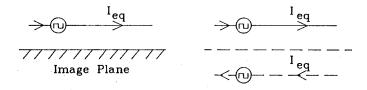

Now assume that a conducting plane is placed beneath a pair of identical parallel PCB traces, such that each trace is parallel to the conducting plane, and the distance between each trace and the plane is h as shown in Figure 4a. Also assume that there is no electrical connection between the traces and the plane. By image theory, the traces and the

conducting plane are equivalent to the four-trace system in Figure 4b, where the image currents flow in the opposite direction of the original currents [14]. The voltages developed across the original traces now become

$$V_1 = L_{p11} \frac{dI_1}{dt} - L_{p12} \frac{dI_2}{dt} - L_{p13} \frac{dI_3}{dt} + L_{p14} \frac{dI_4}{dt}$$

(9a)

$$V_2 = L_{p22} \frac{dI_2}{dt} - L_{p21} \frac{dI_1}{dt} - L_{p24} \frac{dI_4}{dt} + L_{p23} \frac{dI_3}{dt}.$$

(9b)

If  $h \ll l$ , equation (7) can be rewritten to obtain the partial mutual-inductances between the PCB traces and the images, which are

$$L_{p13} = L_{p24} = \frac{\mu_0 l}{2\pi} \left[ \ln \frac{l}{h} - 1 + \frac{2h}{l} \right]$$

(10)

$$L_{p14} = L_{p23} = \frac{\mu_0 l}{2\pi} \left[ \ln \frac{2l}{r} - 1 + \frac{r}{l} \right]$$

(11)

where  $r = \sqrt{d^2 + 4h^2}$ . Because  $I_1 = I_2 = I_3 = I_4 \equiv I$ , we can again define the net partial inductance of each trace, which become

$$L_{p1} = L_{p11} - L_{p12} - L_{p13} + L_{p14}$$

(12a)

$$L_{p2} = L_{p22} - L_{p21} - L_{p24} + L_{p23}$$

(12b)

where  $L_{p1} = L_{p2}$ . These net partial inductances can now be found by substituting (6),(7) and (10),(11) into (12), which gives

$$L_{p1} = L_{p2} = \frac{\mu_0 l}{2\pi} \left[ \ln \frac{4d}{w} - \ln \frac{r}{2h} + \frac{r - d - 2h}{l} \right]$$

(13a)

$$L_{p1} = L_{p2} \simeq \frac{\mu_0 l}{2\pi} \left[ \ln \frac{8h}{w} \right] \qquad if \quad h \leqslant d.$$

(13b)

The effect of the conducting plane can be clearly seen by comparing the net partial inductance of one trace, without the plane (8), to the net partial inductance with the plane (13). This comparison shows that placing a conducting plane beneath a PCB can cause a significant reduction in the ground-noise voltage developed across the net partial inductance of a trace. Moreover, if the distance between the signal and ground-return traces is much larger than the distance h between the traces and the conducting plane, the ground-noise voltage is the same as the voltage that would occur if the distance between the signal and ground-return traces was 2h. In other words, ground-noise problems caused by poorly placed ground-return traces can be corrected by placing a conducting

plane beneath and close to the PCB. Because the result achieved with the conducting plane is caused entirely by the equivalent current images, we call it an *image plane*.

Figure 4. Image Plane beneath PCB Traces and the Equivalent Image System

#### **GROUND-NOISE VOLTAGE**

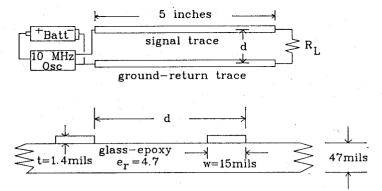

To investigate the effect of an image plane upon ground noise, we constructed a PCB. It included identical parallel traces, a 10 MHz oscillator, a battery, and a load resistor as shown in Figure 5. The PCB was etched with two signal traces and one ground-return trace. The signal traces were connected to the oscillator and the load resistor, one at a time, which resulted in PCB circuits with  $d = 15.2 \, mm$  (600 mils) and  $d = 2.5 \, mm$  (100 mils). These circuits simulated relatively good and bad PCB layouts, respectively. To determine the effect of an image plane, a 10.8 cm (4.25 inch) wide and 21.6 cm (8.5 inch) long piece of copper foil was centered beneath the PCB such that the distance from the traces to the copper foil was 2.4 mm (3/32 inch).

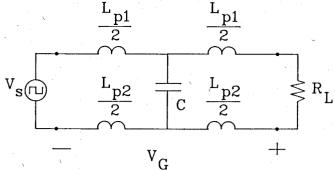

One possible lumped-circuit model for the PCB [8] is shown in Figure 6. Table I lists the net partial inductances for this equivalent circuit that were calculated using equations (8a) and (13a). Note that the use of high-frequency partial inductance formulas was appropriate because of the 10 MHz oscillator. The transmission-line characteristic impedance and

TABLE I

Calculated Net Partial-Inductance of PCB Traces

| Net Partial-Inductance $L_{p1} = L_{p2}$ (nH) |            |                      |             |  |  |  |

|-----------------------------------------------|------------|----------------------|-------------|--|--|--|

| PCB without Image Plane                       |            | PCB with Image Plane |             |  |  |  |

| d = 15.2  mm                                  | d = 2.5 mm | d = 15.2  mm         | d = 2.5  mm |  |  |  |

| 125.9                                         | 82.9       | 97.4                 | 79.8        |  |  |  |

Figure 5. PCB Used to Investigate Ground Noise and Radiated Emissions

capacitance for this circuit can be calculated if the image plane is not present [15], [16]. They are  $403~\Omega$  and 1.56~pF for d=15.2~mm, and  $249~\Omega$  and 2.71~pF for d=2.5~mm. If the image plane is present, the exact calculation of the transmission-line characteristic impedance and capacitance is difficult. However, it is clear that the image plane will increase the total capacitance because it introduces capacitance between each trace and the image plane in parallel with the capacitance between the traces. Because a lumped transmission-line model is accurate if the length of the line is less than  $\lambda/10~[17]$ , the equivalent circuit in Figure 6 is useful up to 236~MHz or the 23rd harmonic of the oscillator.

The peak-to-peak differential ground-noise voltage developed across the entire ground-return trace was measured using a Tektronix P6046 active differential probe and a Tektronix 2467 oscilloscope [1]. Table II lists the results. Several interesting conclusions can be drawn from these measurements.

The ground-noise voltage was  $710\,mV$  without the image plane for  $d=15.2\,mm$  and  $R_L=600\,\Omega$ . Suppose this ground-noise voltage needed to be reduced. Because the characteristic transmission-line impedance of the PCB traces is  $403\,\Omega$ , one might consider matching  $R_L$  to this impedance. But as can be seen from Table II, lowering the load resistance to  $400\,\Omega$  increased the ground noise to  $860\,mV$ . Further examination of Table II reveals that lowering the load resistance increased the ground noise in all cases. This is because lowering the load resistance increased the current, which increased the ground-noise voltage because  $V_G=L\,di/dt$ . This is also one reason why series resistors are effective in solving EMC problems. They reduce the current which, in turn, reduces the ground-noise voltage.

TABLE II

Measured Ground-Noise Voltages

|              | Peak-to-Peak Differential Voltage $V_G(mV)$ |            |                      |            |  |

|--------------|---------------------------------------------|------------|----------------------|------------|--|

|              | PCB without Image Plane                     |            | PCB with Image Plane |            |  |

| $R_L$ (Ohms) | d = 15.2  mm                                | d = 2.5 mm | d = 15.2 mm          | d = 2.5 mm |  |

| 1200         | 560                                         | 550        | 460                  | 420        |  |

| 600          | 710                                         | 580        | 540                  | 450        |  |

| 400 .        | 860                                         |            | 660                  | ***        |  |

| 300          | 1000                                        | 710        | 780                  | 600        |  |

Figure 6. Equivalent Circuit for the PCB

Although increasing the load resistance lowered the ground-noise voltage, one might be concerned that intentionally mismatching the characteristic impedance with the load resistance might cause reflections that would distort the signal across the load. The mismatch causes reflections. However, these reflections do not cause distortion if  $l < 9 t_r$ , where l is the line length in centimeters and  $t_r$  is the signal rise-time in nanoseconds, as discussed on pages 308-309 in [5]. The signal across the load is undistorted because all of the reflections effectively have the same phase as the incident wave. Indeed, the lower ground-noise voltage actually improves the signal quality.

The effect of the image plane on ground-noise voltage can clearly be seen from the measurements listed in Table II. The ground-noise voltage was less with the image plane than without it in all cases. The image plane also corrected the excessive ground noise caused by a poor PCB layout. For example, the ground noise was  $710\,mV$  without the image plane for  $d=15.2\,mm$  and  $R_L=600\,\Omega$ . Reducing the distance between the traces to 2.5 mm did reduce the ground noise to  $580\,mV$  as expected [1], [7]. However, placing the image plane beneath the PCB reduced the ground noise to  $540\,mV$ . In practice, the use of an image plane could eliminate the need for a new PCB layout. Moreover, decreasing the distance between the traces, along with the use of the image plane, further reduced the ground noise to  $450\,mV$ .

The effect of the image plane can be predicted using the data in Table I. The net partial inductance of the ground trace for  $d = 15.2 \, mm$  was  $125.9 \, nH$  without the image plane and  $97.4 \, nH$  with the image plane. If the current through the capacitor in Figure 6 is negligible compared with the load current, the introduction of the image plane will cause the same percentage change in the ground-noise voltage as in the net partial inductance. The measured and calculated ground-noise voltages are listed in Table III for  $d = 15.2 \, mm$  with the image plane placed beneath the PCB. Note that the agreement between calculated and measured results improved with decreasing  $R_L$  (increasing load current) as expected.

Finally, compare the ground-noise voltages listed in Table II for the PCB without the image plane. The change in ground-noise voltage that resulted from reducing the trace separation was a strong function of  $R_L$ . This somewhat unexpected outcome was the result of the increased capacitance caused by the smaller separation distance which, in turn,

TABLE III

Calculated and Measured GroundNoise Voltages for a PCB with an

Image Plane and  $d = 15.2 \, mm$ .

|                       | Ground Noise V <sub>G</sub> (mV |          |  |

|-----------------------|---------------------------------|----------|--|

| R <sub>L</sub> (Ohms) | Calculated                      | Measured |  |

| 1200                  | 434                             | 460      |  |

| 600                   | 550                             | 540      |  |

| 400                   | 666                             | 660      |  |

| 300                   | 775                             | 780      |  |

caused an increase in the total source current that offset the lower net partial inductance of the ground trace. This phenomenon was more pronounced with the larger values of load resistance that were comparable to the impedance of the capacitor. However, for  $R_L=1200\,\Omega$ , reducing the distance between the traces had little effect upon the ground-noise voltage, whereas placing an image plane beneath and close to the PCB caused a significant reduction.

# RADIATED EMISSIONS

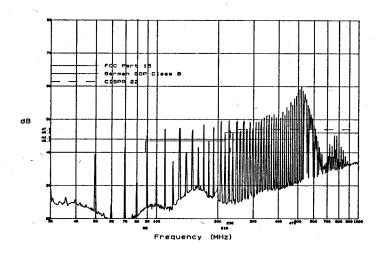

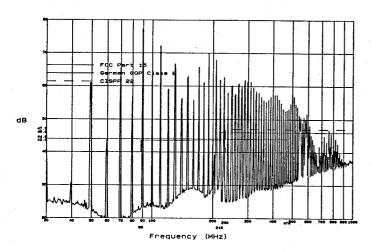

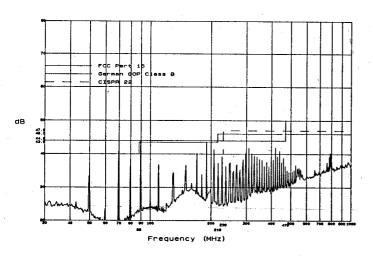

In addition to reducing ground noise, an image plane can also reduce PCB radiation. To investigate this effect, we measured the emissions from the PCB in Figure 5 with  $d = 15.2 \, mm$  and  $R_L = 300 \,\Omega$ . The measurements were performed in a semianechoic chamber using an HP 8568 spectrum analyzer. The PCB was located 1.0 m above the chamber ground-plane and 3.0 m from the receive antenna. All measurements were performed with the spectrum analyzer in peak-hold mode while the table was rotated 360° and the receive-antenna height was scanned from 0.5 to 1.5 meters. Although both the vertically and horizontally polarized electric-fields were measured, only the horizontal measurements were reported because they were larger than the vertical measurements in all cases. This was because both the PCB and the attached wire were parallel to the floor. Had the wire been draped over the edge of the table, the vertical emissions would have been predominant.

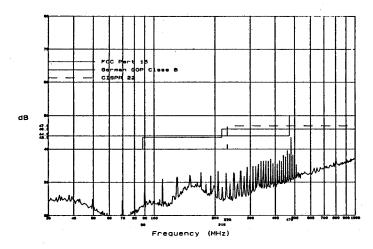

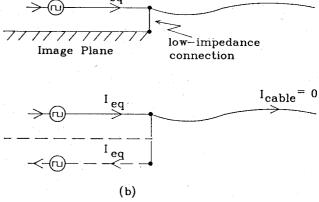

Figure 7 shows the radiated emissions from the PCB alone. Note that even this simple circuit fails to comply with the FCC Part 15 and the CISPR-22 Class-B limits. To reduce these excessive emissions, an image plane was placed beneath and close to the PCB, as it was for the ground-noise measurements. Figure 8 shows the results. The image plane caused a dramatic reduction in the emissions, even though it was not electrically connected to the PCB. Because the image plane caused a greater reduction in the radiated emissions than in the ground-noise voltage (see Table II), the lengths of the wires between the oscillator and the PCB traces were clearly unequal, which caused the PCB to radiate as an asymmetrical dipole antenna, as discussed earlier. This dramatic reduction was caused by the image of the asymmetrical-dipole current  $l_{eq}$  as shown in Figure 9. The image current flowed in the opposite direction of the original PCB current and produced fields that tended to cancel the fields from the original current.

Figure 7. Radiated Emissions from PCB

Figure 8. Radiated Emissions from PCB with Image Plane

Figure 9. Image Plane beneath PCB and Equivalent Image System

Although not shown in Figure 9, the images of the differential-mode currents also produced fields that tended to cancel the fields from the original differential-mode currents.

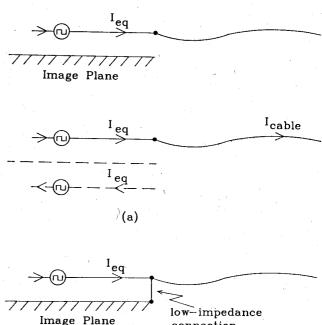

To simulate a peripheral cable that would be connected to the PCB in a typical product, a 1.0 m wire was connected to the PCB ground-return trace shown in Figure 5 at the point where the trace was connected to the load resistor. The wire was stretched horizontally such that it appeared as an extension of the ground-return trace. As shown in Figure 10, the wire increased the emissions from the PCB as expected. The

Figure 10. Radiated Emissions from PCB and Attached Wire

Figure 11. Radiated Emissions from PCB and Attached Wire with Image Plane

image plane was again placed beneath and close to the PCB, and a short wire was connected between the image plane and the ground-return trace at the same point where the 1.0 m wire was connected. Figure 11 shows the results. The image plane again caused a dramatic reduction in the radiated emissions. However, without the connection between the image plane and the PCB, this dramatic reduction did not occur because the image plane then created only a partial image of the total common-mode current as illustrated in Figure 12a. When the image plane was connected to the PCB as depicted in Figure 12b, the image current subtracted from the PCB current, which caused the current on the cable to be dramatically reduced.

In practice, both signal and ground-return wires must be connected to the image plane. In this case, a small-value capacitor can be connected between each signal wire and the image plane. It is important that these capacitors provide a low-impedance connection at the emission frequencies. However, each capacitor value should be chosen such that the integrity of the differential-mode signal currents is assured, which is achievable for most applications.

Figure 12. Connection between Image Plane and PCB with Attached Wire

# CONCLUDING REMARKS

We have shown that the predominant radiation from a PCB, with or without an attached cable, is the result of common-mode current. This current can be produced by the voltage developed across the inductance of the ground-return trace driving the cables as a dipole antenna. For the PCB that we investigated, the common-mode current was caused primarily by a source proportional to the signal voltage driving the traces and the cable as an asymmetric dipole antenna. Moreover, the PCB was an effective common-mode antenna even without the cable.

We also used the concept of partial inductance to calculate the inductance of the ground-return trace. After presenting several useful inductance formulas, the effect of placing an image plane beneath and close to a PCB was shown. The image plane caused a reduction in the ground-noise voltage that was developed across the net partial inductance of the ground-return trace, even though the image plane was not electrically connected to the PCB traces. Increasing the load resistance also lowered the ground-noise voltage, despite the load resistance becoming greater than the transmission-line characteristic impedance,

Finally, we showed that the image plane dramatically reduced the radiated emissions from a PCB, even though the plane was not electrically connected to the PCB. The image plane also dramatically reduced the emissions from a PCB with an attached cable, when the image plane was correctly connected to the PCB.

#### **ACKNOWLEDGMENTS**

The authors thank Homer J. Gardner of IBM Boulder for the numerous discussions that inspired this paper. They also thank Donald R. Bush of IBM Lexington for assisting with the measurements and Dr. Edward F. Kuester of the University of Colorado for his helpful comments.

# REFERENCES

- [1] R.F. German, "Use of a Ground Grid to Reduce Printed Circuit Board Radiation," 6th Symposium and Technical Exhibition on Electromagnetic Compatibility, Zurich, March 5-7, 1985, pp. 133-138.

- [2] C.R. Paul, "A Comparison of the Contributions of Common-Mode and Differential-Mode Currents in Radiated Emissions," *IEEE Transactions on Electromagnetic Compatibility*, Vol. 31, No. 2, May 1989, pp. 189-193.

- [3] C.R. Paul and D.R. Bush, "Radiated Emissions from Common-Mode Currents," *IEEE International Symposium on Electromagnetic Compatibility*, Atlanta, Georgia, August 25-27, 1987, pp. 197-203.

- [4] R.C. Hansen, "Fundamental Limitations in Antennas," Proceedings of the IEEE, Vol. 69, No. 2, February 1981, pp. 170-182.

- [5] H.W. Ott, Noise Reduction Techniques in Electronic Systems (second edition). New York: John Wiley Interscience, 1988.

- [6] W.L. Wecks, Antenna Engineering. New York: McGraw-Hill, 1968, pp. 161-184.

- [7] H.W. Ott, "Digital Circuit Grounding and Interconnection," IEEE International Symposium on Electromagnetic Compatibility, Boulder, Colorado, August 18-20, 1981, pp. 292-297.

- [8] C.R. Paul, "Modeling Electromagnetic Interference Properties of Printed Circuit Boards," IBM Journal of Research and Development, Vol. 33, No. 1, pp. 33-50, January 1989.

- [9] A.E. Ruchli, "Inductance Calculations in a Complex Environment," *IBM Journal of Research and Development*, Vol. 16, No. 5, pp. 470-481, September 1972.

- [10] C.R. Paul, Analysis of Linear Circuits. New York: McGraw-Hill, 1989.

- [11] F.W. Grover, Inductance Calculations, Working Formulas and Tables. Research Triangle Park, North Carolina: Instrument Society of America, 1973, pp. 33-35.

- [12] C.T.A. Johnk, Engineering Electromagnetic Fields and Waves. New York: John Wiley and Sons, 1975, pp. 318-322.

- [13] P.L. Kalantarov and L.A. Tseitlin, Calculation of Inductance (third edition). [Russian:], Leningrad: Energoatomizdat, 1986, pp. 102-104.

- [14] C.R. Paul and S.A. Nasar, Introduction to Electromagnetic Fields. New York: McGraw-Hill, 1987, pp. 599-608.

- [15] K.C. Gupta, R. Garg, and I.J. Bahl, Microstrip Lines and Slotlines. Dedham, MA: Artech House, 1979.

- [16] A.E. Ruehli and P.A. Brennan, "Efficient Capacitance Calculations for Three-Dimensional Multiconductor Systems," *IEEE Transactions* on Microwave Theory and Techniques, Vol. MTT-21, February 1973, pp. 76-82.

- [17] W.W. Everett, "Lumped Model Approximations of Transmission Lines: Effect of Load Impedances on Accuracy," *IEEE International Symposium on Electromagnetic Compatibility*, Washington, D.C., August 23-25, 1983, pp. 441-445.